Mathis77

#0

http://sharikou.blogspot.com/2...

tja, jeg tror ikke engang det er en AMD-fanatiker, der har skrevet det, men C2D, C2Q og fremtidige intel-roadmaps bliver da haglet ned...

lidt tyndt...men har skribenten ret?

Og glædelig jul

tja, jeg tror ikke engang det er en AMD-fanatiker, der har skrevet det, men C2D, C2Q og fremtidige intel-roadmaps bliver da haglet ned...

lidt tyndt...men har skribenten ret?

Og glædelig jul

#1

Tror han er Stor Amd fan... Han kan vel ha ret i noget af det omkring den måde de er bygget på.. Kan sikkert godt være de er gammel dags bygget op. Men hey lortet er stadig 10 gange hurtigere end amd´s nuværende cpu´er så.

#2

Han har sådan set ret, AMD dual core design er noget mere effektiv uden jeg vil komme nærmere ind på struktur og instruktionssæt, og Intel bygger på samme teknologi. Men sålænge ydelsen er i Intel chippen så er der intet at komme efter... endnu.

#1: Det er nu en overdrivelse.

#1: Det er nu en overdrivelse.

#3

Overdrivelse fremmer forståelsen!! ;)

#4

Prøv at kigge på datoen for bloggen! Desuden er han AMD fan!

/Lars

/Lars

#5

Sharikou? Han er verdens største AMD fanatiker..

Jeg vil ikke tage hans spekulationer for noget som helst..

Jeg vil ikke tage hans spekulationer for noget som helst..

#6

Intel kommer faktisk med indbygget memory controller indenfor et par år :)

http://hwt.dk/news.asp?id=1302...

Intel's næste socket LGA 1366 kommer med memory controller, ca. 2008.

http://hwt.dk/news.asp?id=1302...

Intel's næste socket LGA 1366 kommer med memory controller, ca. 2008.

#7

lidt morsomt at in tel skulle være så dårlig når den slår amdén i alt.

Så han er amd fanboy , fik en meget lang forklaring fra en intel rep om hvad forskellen er på en amd og en c2d, nu var det en intel rep så han var nok lidt farvet :)

men en c2d er bygget noget anderledes op end en pentium d,

en af fordelene ved c2d frem for de gamle pentiumd er at en conroe kan en kærne udnytte hele cashen hvor de gamle pentium d kune den kun bruge den ene halvdel.

Så han er amd fanboy , fik en meget lang forklaring fra en intel rep om hvad forskellen er på en amd og en c2d, nu var det en intel rep så han var nok lidt farvet :)

men en c2d er bygget noget anderledes op end en pentium d,

en af fordelene ved c2d frem for de gamle pentiumd er at en conroe kan en kærne udnytte hele cashen hvor de gamle pentium d kune den kun bruge den ene halvdel.

#8

Jamen det som manden klager over har Intel da lige rettet? De to kerner ved de sidder ved siden af hinanden, og skal IKKE kommunikere med hinanden gennem FSB`en, men bare gennem cachen... Som #7 siger så kan de dele data mellem dem gennem kernen, det er netop dette manden kritisere... Men det er nu løst og det er bla derfor conroe er så sindsygt :)

Shake

Shake

#9

Det var da en noget smal synet konklusion....

Men som #7 og #8 påpeger, så kan Core arkitekturen jo dynamisk tildele cachen, til hver enkelt core i cpu'en. Om den så kan bruge dette til at kommunkere immelem de forskellige cores, skal jeg ikke kunne udtale mig om, og ved slet ikke om der er et behov for at dele data imellem helt ens cores inde i cpu'en? (måske er det bare et waste of cpu cycles?)

Det samme kan jo så også gøre sig gældende mht. memory controlleren, at Intel måske finder det bedre med én samlet ram, istedetfor at spære dele af den totale mængde inde i et bur med hver sin core...

Til det skal måske lægges vægt på Intels I/OAT teknologi, som benytter 2stk. FSB, og dermed fordobler båndbredden ned til memory controlleren...

Men som #7 og #8 påpeger, så kan Core arkitekturen jo dynamisk tildele cachen, til hver enkelt core i cpu'en. Om den så kan bruge dette til at kommunkere immelem de forskellige cores, skal jeg ikke kunne udtale mig om, og ved slet ikke om der er et behov for at dele data imellem helt ens cores inde i cpu'en? (måske er det bare et waste of cpu cycles?)

Det samme kan jo så også gøre sig gældende mht. memory controlleren, at Intel måske finder det bedre med én samlet ram, istedetfor at spære dele af den totale mængde inde i et bur med hver sin core...

Til det skal måske lægges vægt på Intels I/OAT teknologi, som benytter 2stk. FSB, og dermed fordobler båndbredden ned til memory controlleren...

#10

#7/#8/#9 Den dualcore han snakker om er D8xx/D9xx, se på datoen

/Lars

/Lars

#11

#10 Det er også det vi snakker om :) Manden har tydeligvis ikke læst intels roadmaps dengang.. = Spade = Man skal ikke tage hans mening for noget!

Shake

Shake

#12

#11 Det er korrekt det meste af det han siger, han udelader bare meget vigtige informationer bla. omkring conroe!

/Lars

/Lars

#13

#7 Intel slår ikke amd i alt🙂 Intel er god til spil især i windows xp, men snakker vi vista, så tror jeg ikke den slår amd så meget enda, selvom den er da god nok.

#14

#12 At udelade meget vigtige oplysninger er også at lyve! Især når han påstår at Intel ikke har noget der yder ordenligt iforholdtil AMD!

Shake :)

Shake :)

#15

#14 på det tidspunkt havde intel ikke core2duo, så intel var noget skidt dengang.

Prøv du at sidde ved en pentium 4 eller en Pentium D, så ved du hvad jeg mener. Jeg har så kun selv ejet en pentium 4 3,6 ghz - Men det var også slemt nok. En ven købte Pentium D, og det gjorde ikke indtrykket bedre.

Glæd jer over at nu er der core2duo🙂 og Athlon 64 X2. Så længe der er konkurence, så er der lave priser på CPU'erne🙂

Prøv du at sidde ved en pentium 4 eller en Pentium D, så ved du hvad jeg mener. Jeg har så kun selv ejet en pentium 4 3,6 ghz - Men det var også slemt nok. En ven købte Pentium D, og det gjorde ikke indtrykket bedre.

Glæd jer over at nu er der core2duo🙂 og Athlon 64 X2. Så længe der er konkurence, så er der lave priser på CPU'erne🙂

#16

#15 Sidder ved det nu, og den kører bedre end alt andet jeg har siddet ved?

Shake

Shake

#17

AMD er vist næsten ligeså stærk som Intel i 64bit.. Netop denne fight glæder jeg mig til at høre mere om.

Men intels dynamiske cache er netop en kæmpe fordel ved nuværende single-tråds spil. Ved brug af begge core vil intel muligvis få en del mere konkurrence fra AMD's X2-serie.

Men det er som sagt ikke nutiden, og CPU'er holder som ofte max 4-5år og i vore kredse ofte ikke længere end 2år.

Huske at nogle Core2 også snakker med hinanden gennem fsb, altså når vi snakker Quad-core. Kentsfield er ikke mere end 2 Conroe, på samme måde som PentiumD ikke er andet end 2 Prescott/cedar mill

l :00 :(

AMD har så en meget lille cache til forskel fra Intel (AMD tjener kassen på det) Men AMD har bygget deres CPU'er til DDR-ram, og DDR2 samt DDR3 har en høj latency, dvs. at den hurtigere cache er vigtigere, og AMD for fremtiden også må se at få smækket noget mere cache på deres CPU'er. en Athlon X2 med 4MB cache kunne sagtens gå hen og blive temmelig ond med DDR2 ram :)

Men intels dynamiske cache er netop en kæmpe fordel ved nuværende single-tråds spil. Ved brug af begge core vil intel muligvis få en del mere konkurrence fra AMD's X2-serie.

Men det er som sagt ikke nutiden, og CPU'er holder som ofte max 4-5år og i vore kredse ofte ikke længere end 2år.

Huske at nogle Core2 også snakker med hinanden gennem fsb, altså når vi snakker Quad-core. Kentsfield er ikke mere end 2 Conroe, på samme måde som PentiumD ikke er andet end 2 Prescott/cedar mill

l :00 :(

AMD har så en meget lille cache til forskel fra Intel (AMD tjener kassen på det) Men AMD har bygget deres CPU'er til DDR-ram, og DDR2 samt DDR3 har en høj latency, dvs. at den hurtigere cache er vigtigere, og AMD for fremtiden også må se at få smækket noget mere cache på deres CPU'er. en Athlon X2 med 4MB cache kunne sagtens gå hen og blive temmelig ond med DDR2 ram :)

#18

Pentium D og almindelig Pentium køre ikke bedre end amd maskinerne fra samme tidsrum tværtimod, sorry. Du skal over i core2duo for at få noget godt fra intel.

Selvfølge er det da ikke være, end maskinerne køre fint nok, de er bare dårligere og fordi en maskine er 20% langsommere til et eller andet og måske bruger 50 watt mere gør ikke noget hvis bare den ikke står tændt 24 timer i døgnet🙂

Så jo de køre udenmærket🙂

Hvis du ser hvordan folk sammenligner core2duo med amd's athlon X2 og der er ikke ret meget ydelses foreskel, så er de gamle pentium'er meget dårlige i forehold til Athlon 64 og Pentium D i forehold til athlon 64 X2. og alligevel kan de jo sagens bruges og er slet ikke så slemme🙂 det samme gælder en overclocket amd mod en overclocket core2duo, selvom core2duo er lidt hurtigere, køre amd'en ganske udenmærket🙂

Selvfølge er det da ikke være, end maskinerne køre fint nok, de er bare dårligere og fordi en maskine er 20% langsommere til et eller andet og måske bruger 50 watt mere gør ikke noget hvis bare den ikke står tændt 24 timer i døgnet🙂

Så jo de køre udenmærket🙂

Hvis du ser hvordan folk sammenligner core2duo med amd's athlon X2 og der er ikke ret meget ydelses foreskel, så er de gamle pentium'er meget dårlige i forehold til Athlon 64 og Pentium D i forehold til athlon 64 X2. og alligevel kan de jo sagens bruges og er slet ikke så slemme🙂 det samme gælder en overclocket amd mod en overclocket core2duo, selvom core2duo er lidt hurtigere, køre amd'en ganske udenmærket🙂

#19

Ups det var til #17 🤡 Har jeg lagt mærke til i altid skriver🙂

#21

#17 giver dig ret i det første🙂

Men! En amd med meget cache vil ikke blive ond, fordi vores socket am2 er rimeligt god og kan nå at overføre det nødvendige. Mit skift fra 1mb L2 tli 2mb L2 kunne jeg ikke andet end lige mærke fordi delene er så velkørende sammen, hvis jeg havde haft et dårligt bundkort, så havde jeg måske mærket det mere🙂 jeg er sikker på at 4mb cache vil jeg ikke kunne mærke🙂

Intel derimod har ikke en super socket ligesom deres memory controller ligger på motherboardet og derfor bliver de nød til at ha' en højre cache🙂

Men! En amd med meget cache vil ikke blive ond, fordi vores socket am2 er rimeligt god og kan nå at overføre det nødvendige. Mit skift fra 1mb L2 tli 2mb L2 kunne jeg ikke andet end lige mærke fordi delene er så velkørende sammen, hvis jeg havde haft et dårligt bundkort, så havde jeg måske mærket det mere🙂 jeg er sikker på at 4mb cache vil jeg ikke kunne mærke🙂

Intel derimod har ikke en super socket ligesom deres memory controller ligger på motherboardet og derfor bliver de nød til at ha' en højre cache🙂

#22

Det hele handler om latency eller den forsinkelse der er til rammene... DDR2 og DDR3 er virkelig langsomme.. dvs. fra CPU'en kalder på rammene, til den for svar og data, tager ofte dobbelt så langt tid med DDR2/3 frem for de gamle DDR1-ram. Dvs. en lille cache gør ikke noget, da rammene giver hurtig respons. Netop derfor er AM2 sjældent hurtigere end 939.

Intel derimod, har to problemer.. ekstern memory-controller og DDR2/3-ram. det giver rigtig høj latency. Derfor den høje cache. Med DDR2/3 har AMD logisk set også brug for mere cache, men for at spare penge har AMD nok set igennem finger med det i første omgang.

Jeg tror heller ikke du kan mærke forskel fra en Core2 og en athlonX2 uden videre. Forskellen er faktisk ret marginal, men til core2's fordel. Måske vil en 4MB cache-X2'er fjerne den forskel og gøre X2 ca. lige hurtig. Dernæst er der self oc-potentialle, som de fleste alligvel sjældent benytter sig af.

Og igen 64bit... Microsoft har bl.a. nævnt at AMD's processorer er rigtig gode til det.... uden at nævne hvem der var knap så gode.

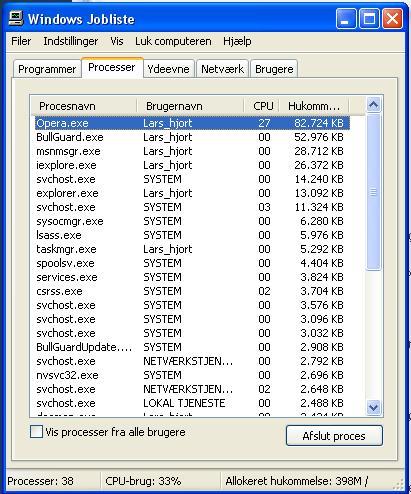

PentiumD er dog en sinke og derfor var singleCore med HT ofte bedre til det simple multitasking som windows end en dualcore pentiumD.

Intel derimod, har to problemer.. ekstern memory-controller og DDR2/3-ram. det giver rigtig høj latency. Derfor den høje cache. Med DDR2/3 har AMD logisk set også brug for mere cache, men for at spare penge har AMD nok set igennem finger med det i første omgang.

Jeg tror heller ikke du kan mærke forskel fra en Core2 og en athlonX2 uden videre. Forskellen er faktisk ret marginal, men til core2's fordel. Måske vil en 4MB cache-X2'er fjerne den forskel og gøre X2 ca. lige hurtig. Dernæst er der self oc-potentialle, som de fleste alligvel sjældent benytter sig af.

Og igen 64bit... Microsoft har bl.a. nævnt at AMD's processorer er rigtig gode til det.... uden at nævne hvem der var knap så gode.

PentiumD er dog en sinke og derfor var singleCore med HT ofte bedre til det simple multitasking som windows end en dualcore pentiumD.

#23

Jeg er enig i mange af trådene. Det er en "ældre" post, men netop fordi den beskriver et roadmap for 2006-08, ved vi jo netop allerede nu, at manden spiser intel-chips-havrefras til morgenmad.

Men det jeg var lidt ude efter var, om intel ku sætte 3-4 memory-controllere i fx. yorkfield-cpuen, som kommer Q3-2007??

synes også conroe (læs: core-teknologien) bliver let og elegant hoppet over... Det er det mest revolutionerende i nyere tid, siden pentium tog livet af 486DXerne.

Med fremtidige chip bliver intel lige så overlegne vil jeg tro. De har også budgettet og de bedste forudsætninger til at lave de bedste ting. Mindre firmaer finder altid små huller i de stores og prøver at lave noget bedre selv og markedsføre det, samtidigt med at de ikke kan andet end det næsten.

Men det jeg var lidt ude efter var, om intel ku sætte 3-4 memory-controllere i fx. yorkfield-cpuen, som kommer Q3-2007??

synes også conroe (læs: core-teknologien) bliver let og elegant hoppet over... Det er det mest revolutionerende i nyere tid, siden pentium tog livet af 486DXerne.

Med fremtidige chip bliver intel lige så overlegne vil jeg tro. De har også budgettet og de bedste forudsætninger til at lave de bedste ting. Mindre firmaer finder altid små huller i de stores og prøver at lave noget bedre selv og markedsføre det, samtidigt med at de ikke kan andet end det næsten.

#24

#22

Nej🙂.. På socket 939 kunne jeg mærke foreskel på om jeg havde 2mb cache eller 1mb cache. Det kan jeg næsten ikke på socket am2, jeg blev lidt skuffet da jeg satte min 2mb cache cpu i, men hvad.. den kan clockes pænt.. mere end hvad jeg allerede har gjordt😀

Bortset fra det har CL noget at sige ja🙂

Nej🙂.. På socket 939 kunne jeg mærke foreskel på om jeg havde 2mb cache eller 1mb cache. Det kan jeg næsten ikke på socket am2, jeg blev lidt skuffet da jeg satte min 2mb cache cpu i, men hvad.. den kan clockes pænt.. mere end hvad jeg allerede har gjordt😀

Bortset fra det har CL noget at sige ja🙂

#25

#ALLE

Man kan ikke mærke forskel fra en AMD X2 og en Conroe fordi de begge er så syge at de trækker nok FPS i spil... Så hvis der kom nogle spil der trækt tænder ud på cpu´en ja så vil man kunne mærke en forskel fra conroe og AMD X2... For en conroe er noget hurtigere, det er bare synd dette potientale ikke bliver udnyttet...

Enige? :)

Shake

Man kan ikke mærke forskel fra en AMD X2 og en Conroe fordi de begge er så syge at de trækker nok FPS i spil... Så hvis der kom nogle spil der trækt tænder ud på cpu´en ja så vil man kunne mærke en forskel fra conroe og AMD X2... For en conroe er noget hurtigere, det er bare synd dette potientale ikke bliver udnyttet...

Enige? :)

Shake

#26

jeg havde mærkbart flere fps i eq2 for et næsten et år siden da jeg gik fra A64 3200+ til opteron170. At gå til core2duo derfra var endnu vildere...langt flere ting kan foregå på skærmen ad gangen og mere flydende... Så både dualcore og generelt core teknik har været alle pengene værd for mig. Jeg har nemlig ikke det vildeste GFX, så jeg går mere op i cpu-ydelse, og jeg må sige, at singlecore er stendød. Næste cpu jeg skal ha skal ha mindst 4 cores... Selvom ikk alt er skrevet til 4core endnu, så får man jo generelt et meget bedre system-feel og respons..

Tak for dansen A64 og glædelig jul 8) :f

Tak for dansen A64 og glædelig jul 8) :f