Test: Intel Core i7 920

CPU, Intel d. 11. december. 2008, skrevet af Polarfar 24 Kommentarer. Vist: 24595 gange.

Korrekturlæser:

Billed behandling:

Oversættelse:

Pristjek på http://www.pricerunner.dk

Produkt udlånt af: Intel

DK distributør: Rosenmeier

Billed behandling:

Oversættelse:

Pristjek på http://www.pricerunner.dk

Produkt udlånt af: Intel

DK distributør: Rosenmeier

#1

Fin artikel 🙂

Det gjorde mig 100% sikker på at det er 920 ´eren jeg skal have.

Var måske lidt skeptisk overfor den 4,8 linie men det lader til at den følger med op når fsb bliver hævet 🙂

Det gjorde mig 100% sikker på at det er 920 ´eren jeg skal have.

Var måske lidt skeptisk overfor den 4,8 linie men det lader til at den følger med op når fsb bliver hævet 🙂

#2

#0

hvis du skulle have tid og mulighed så prøv med 6GB ram det giver rigtig meget i ydelse

hvis du skulle have tid og mulighed så prøv med 6GB ram det giver rigtig meget i ydelse

#3

#2

Vi prøver at skaffe et 6GB kit. Det er ellers et pænt nasty system du har fået banket sammen der 🙂

Vi prøver at skaffe et 6GB kit. Det er ellers et pænt nasty system du har fået banket sammen der 🙂

#4

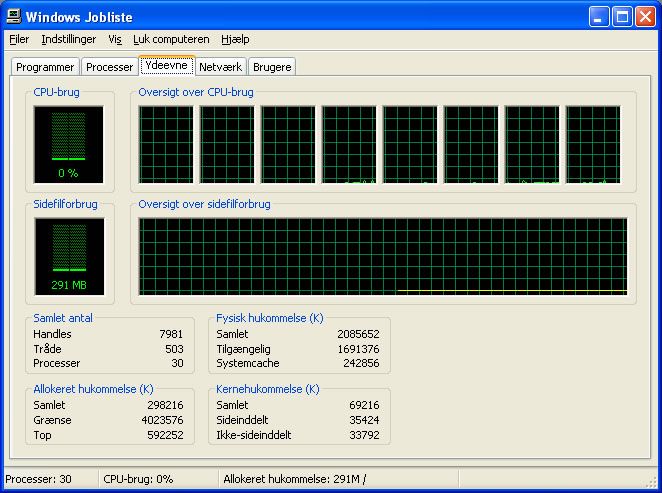

#2 hvor står der at du har 8 proccesore, når nehalm er en quadcore? 😲

#5

0# brug da mere end multi 21 :p

1# pederrs har den højere endnu på vand vist.

2# Hvorfor skulle 3 x 2Gb give bedre end 3 x 1 Gb :)

3# Fordi det den har Hyper-Threating :)

Og det virker enda ret god ydelses mæssigt.

1# pederrs har den højere endnu på vand vist.

2# Hvorfor skulle 3 x 2Gb give bedre end 3 x 1 Gb :)

3# Fordi det den har Hyper-Threating :)

Og det virker enda ret god ydelses mæssigt.

#6

Personligt tror jeg det er netop denne processor phenom II kommer til at kæmpe imod, en billig(forholdsvist) intel high-end CPU. i7 920 skal nok give AMD noget at tænke på. Hvis jeg skulle opgradere CPU og bindkort i dag så ville jeg ligesom #1 vælge denne CPU.

#7

#5

Det er lidt svært at have multi på mere end 21 med i7-920 ;) 20 multi uden turbo mode og 21 med.

Spørgsmål til testen: Er det en retail model i har testet? Hvis ja, har i så kunnet komme over 4 på ram multi?

Det er lidt svært at have multi på mere end 21 med i7-920 ;) 20 multi uden turbo mode og 21 med.

Spørgsmål til testen: Er det en retail model i har testet? Hvis ja, har i så kunnet komme over 4 på ram multi?

#8

#7

Jeg mener nu bestemt jeg så den trække op på 22x med Turbo slået til.

det er er en standard retail cpu. Hvad mener du med over 4 ? Rammene kører 1600MHz, altså 12x multiplier

Jeg mener nu bestemt jeg så den trække op på 22x med Turbo slået til.

det er er en standard retail cpu. Hvad mener du med over 4 ? Rammene kører 1600MHz, altså 12x multiplier

#9

Virkelig god test.. En lille ting jeg dog ikk helt forstår er, kan en i7-965 heller ikk komme op over 4.2 gHz?? undrede mig bare over at han skriver under overclockning at det er det samme som hans 965 kan, og så noget med en spærring der må være på dem... 😕 😕

#10

#9

JEG kan ikke få min 965 over 4.25 lige pt, men jeg mangler nok bare OC skillz 🙂 Verdensrekorden er 5.5GHz med en ordenlig gang LN2 på, så det er ikke umuligt. Meget afhænger af bundkortene og især BIOS.

JEG kan ikke få min 965 over 4.25 lige pt, men jeg mangler nok bare OC skillz 🙂 Verdensrekorden er 5.5GHz med en ordenlig gang LN2 på, så det er ikke umuligt. Meget afhænger af bundkortene og især BIOS.

#11

#8

Jeg har haft i7-920 siden slutningen af oktober, og jeg har aldrig set min være oppe på en multi der hed x22 ?

Jeg har haft i7-920 siden slutningen af oktober, og jeg har aldrig set min være oppe på en multi der hed x22 ?

#12

Jeg synes bare ikke at det er særlig meget for deres extreme processor. Så er der jo ikk særlig meget idé i at købe en 965 når en 920 kan det samme... 😉

#13

Lækker læsning og god test 🙂

#14

Forstår nu ikke hvorfor prisen ikke får 5 :s til prisen er det jo umuligt at få samme ydelse ved mindre du vil ofre 6k ++ =/

#15

#0

God test Polarfar 🙂 - Spændende læsning.

God test Polarfar 🙂 - Spændende læsning.

#16

#14

Du kan få lige så god ydelse både arbejdsmæssigt og spilmæssigt fra en E8500 eller E8600. Det er faktisk først det øjeblik du har brug for multitasking ud over det sædvanlige at en i7 bliver rigtig interessant. Til prisen, og set i forhold til 940 og 965 er den til et femtal, men SÅ meget bedre end en Core 2 er den jo heller ikke.

Du kan få lige så god ydelse både arbejdsmæssigt og spilmæssigt fra en E8500 eller E8600. Det er faktisk først det øjeblik du har brug for multitasking ud over det sædvanlige at en i7 bliver rigtig interessant. Til prisen, og set i forhold til 940 og 965 er den til et femtal, men SÅ meget bedre end en Core 2 er den jo heller ikke.

#17

og jeg er så den eneste der syns, at det er en omgang farvet bøh 😕 men i må ha en god 10. dec. !

#18

God test, men savner ram test i SS sandra og evt. Winrar benchmark score.

hvis det var muligt at tilføje det til testen..

😀

hvis det var muligt at tilføje det til testen..

😀

#19

Jeg tvivler på, at der er indlagt nogen oc begrænsning fra Intels side. Mon ikke nærmere, at Intel har oplevet det samme som AMD - nemlig at et chipdesign med indbygget memorycontroller er ganske kompliceret og giver færre superchips, der kan nå astronomiske oc resultater.

#20

#16 det kan jeg selvfølgelig godt give dig ret i.. Meget god og grundig test 🙂 Godt læsestof.

#21

Jeg kan bekræfte en fremgang på ca. 33% i 3dsmax renderinger. (i forhold til en Q9550). Det må siges at være noget af en forbedring.

#22

Polarfar jeg forstår altså ikke hvorfor i bliver ved med at snakke om en OC sikring? Den er der ikke. I starten var da tale om, at når man overskred TDP så ville man ikke få noget ud af at clocke videre. Det fik bundkort producenterne dog meget hurtig bugt med.

Du skriver ligeledes at CPU'en er låst til multiplier 20, hvilket også er den i bruger. Det passer jo ikke, da du kan slå Turbo funktionen til og dermed få dem op på 21. Jeg har selv en 920 og uden de store problemer fik jeg den op og køre Superpi på 4577MHz med vandkøling. Jeg ved der er en del mere i den, så en 920 clocker ganske udemærket.

Du skriver ligeledes at CPU'en er låst til multiplier 20, hvilket også er den i bruger. Det passer jo ikke, da du kan slå Turbo funktionen til og dermed få dem op på 21. Jeg har selv en 920 og uden de store problemer fik jeg den op og køre Superpi på 4577MHz med vandkøling. Jeg ved der er en del mere i den, så en 920 clocker ganske udemærket.

#23

#22 jeg har et ASUS P6T Del. OC Palm.. kan fint køre 200 x19 på min 940 ES.

Ku være fedt at køre 200x20 med en 920 og så med turbo - det må være mit udgangspunkt når jeg skal hjem og lege i eftermiddag/aften med min nye 920 plus V8 køler 😀

Ku være fedt at køre 200x20 med en 920 og så med turbo - det må være mit udgangspunkt når jeg skal hjem og lege i eftermiddag/aften med min nye 920 plus V8 køler 😀

#24

#23

20x200 kan sagtens lade sig gøre med omkring 1.4 V

20x200 kan sagtens lade sig gøre med omkring 1.4 V